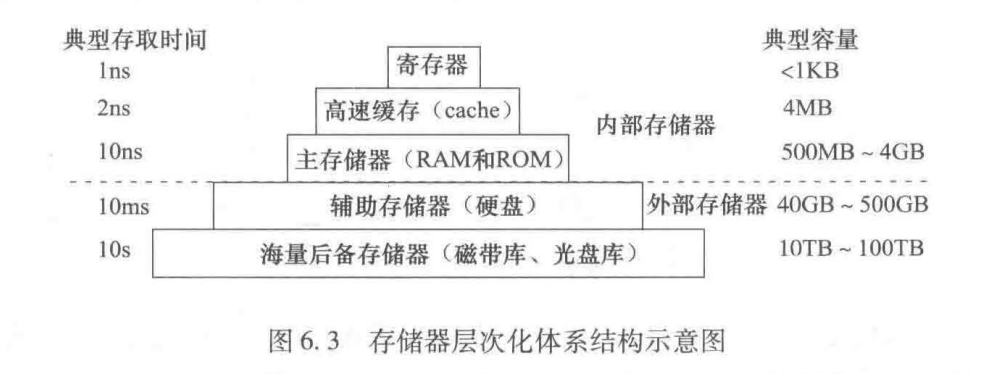

层次结构存储系统

层次结构存储系统

按存取方式分类

RAM(随机存取存储器)

SAM(顺序存取存储器),如磁带

DAM(直接存取存储器),如磁盘

CAM(相联存储器):按照内容访问,如快表

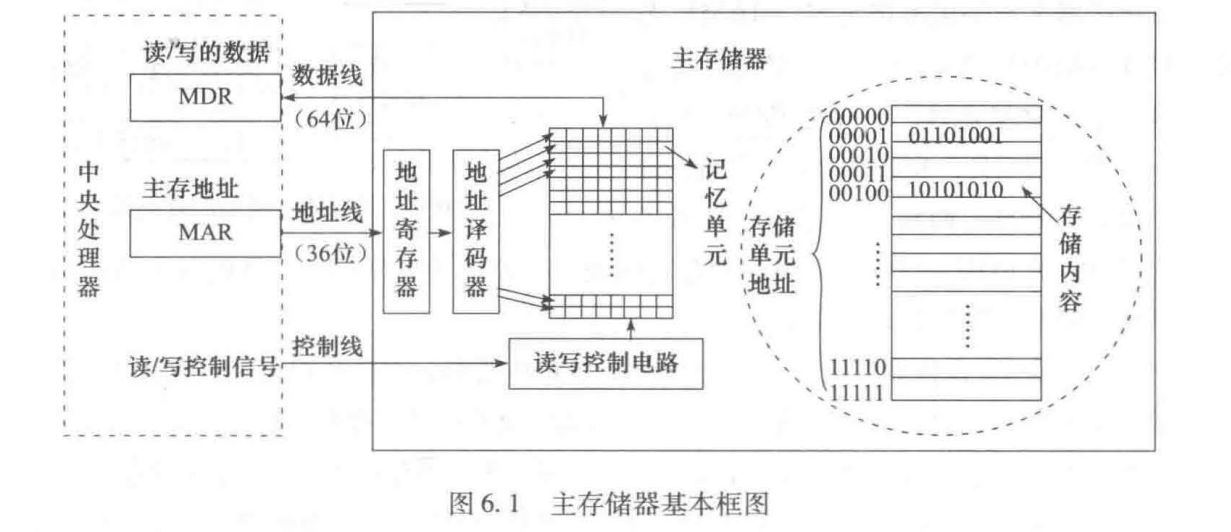

主存储器结构

层次结构

SDRAM芯片技术

该芯片读写受到外部系统时钟(即前端总线时钟CLK)控制,因此与CPU之间采用同步方式交换数据。他将CPU或者其他主设备发出的地址和控制信息锁存起来,经过确定的几个时钟周期后给出响应。

支持突发传输,只要在第一次存取时给出首地址,以后按照地址顺序读写即可

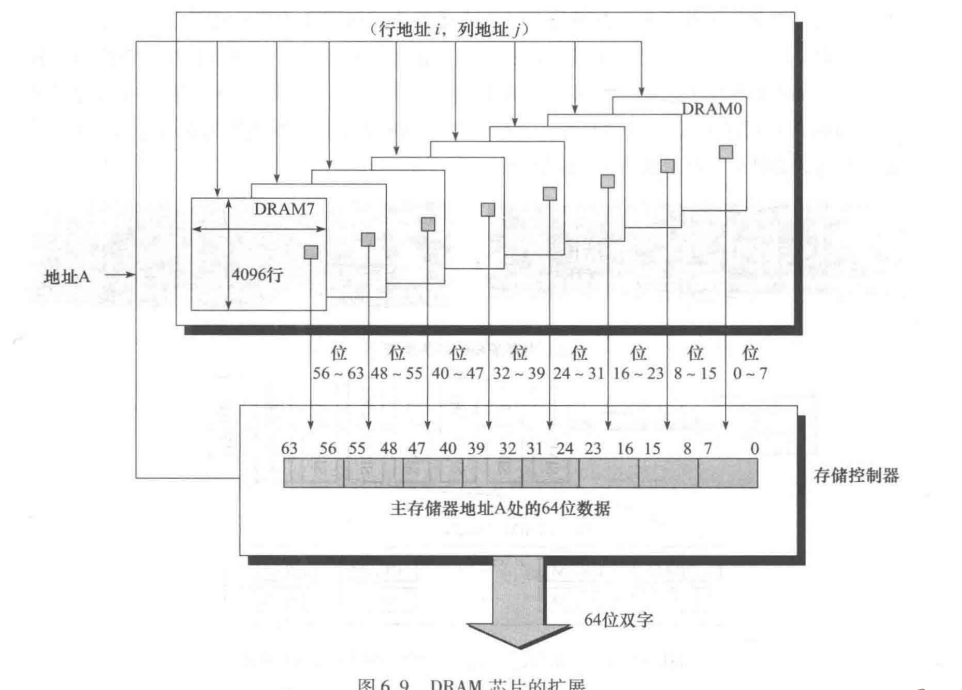

DRAM芯片位扩展

位扩展:用若干片位数较少的存储器芯片构成给定字长的存储器,如下图:

可见,数据读取时是多个字节读取的,如果数据不对齐就需要多次访存,浪费时间

高速缓冲存储器

程序访问的局部性:在较短时间间隔内,程序产生的地址往往集中在存储空间的一个很小范围,这种现象成为程序访问的局部性

时间局部性:多次访问同一个内存地址

空间局部性:访问相邻地址

为了更好利用局部性,通常把当前访问单元以及邻近单元作为一个主存储块一起调入cache

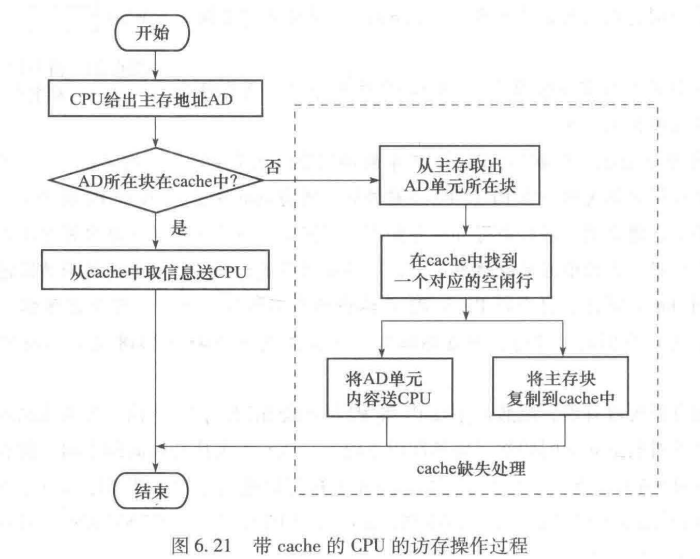

CPU在cache中的访问过程

cache命中:CPU访问单元所在的主存块在cache中

由于程序访问的局部性特点,cache的命中率可以达到很高

cache行和主存块的映射

直接:每个主存块映射到cache固定行,容易导致频繁换入换出

全相联:每个主存块映射到cache任意行,难以操作

组相联映射:将cache分成大小相等的组,每个主存块被映射到cache固定组中的任意一行,即采用组间模映射、组内全映射的方式

cache中的主存替换算法

由于多个主存块会映射到同一个cache行中,因此需要决定将哪个块淘汰掉

先进先出算法:淘汰最先进入的,没有局部性

最近最少用算法:淘汰使用最少的

最不经常用算法

随机替换算法:随机选取一个,性能略差于其他算法,但代价低

cache一致性问题

cache中的内容需要和主存的内容保持同步

写回法:当CPU执行写操作时,如果写命中,则信息只会被写入cache而不会被写入内存;如果没有命中,则在cache中分配一行,将主存块调入该cache行中并更新cache中相应单元的内容

之后cache行中的主存块被替换时,才将该主存块内容一次性写回内存,如果块脏,则写回,否则丢弃

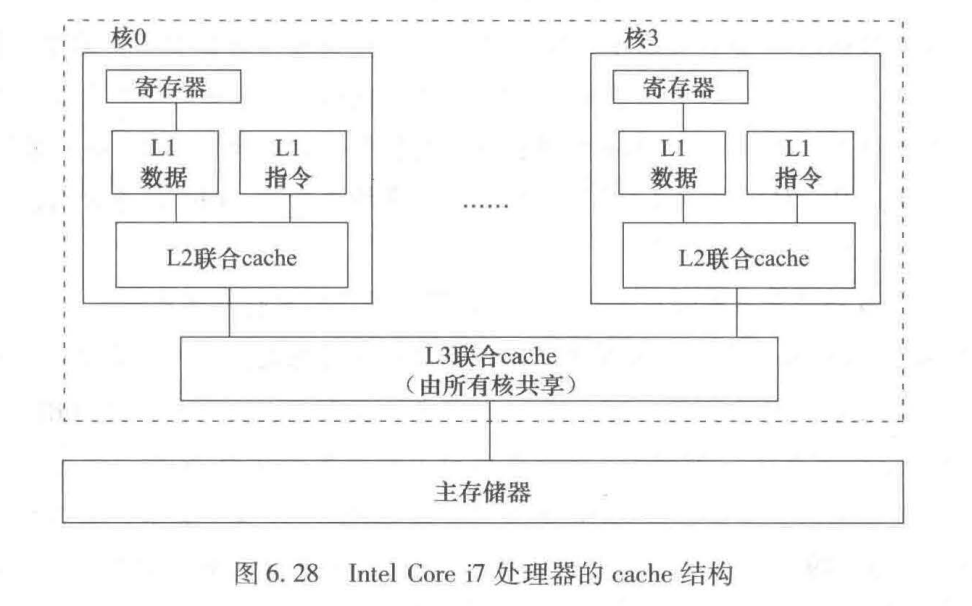

IA-32的cache结构