CPU与程序执行

CPU与程序执行

程序执行过程

- 取指令。将要执行的指令存放在PC中,取出的指令存放到IR中

- 译码。不同指令被翻译成不同的控制信号

- 计算源操作数地址并取操作数。

- 执行数据操作。在操作元件中对取出的操作数进行计算

- 目的操作数地址计算并存结果。

- 指令地址计算并将其送PC。如果是定长指令字,如MIPS指令集,则在第一步取指令的同时计算出下一条指令地址并送PC。此时跳过该步

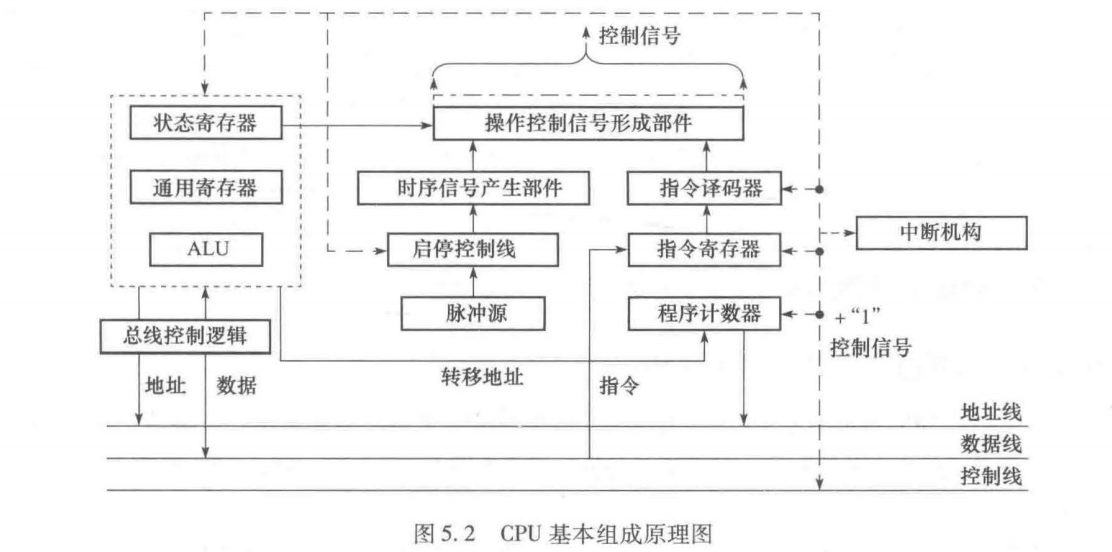

CPU基本功能和组成

- 程序计数器(PC)

- 指令寄存器(IR)

- 指令译码器(ID)

- 启停控制逻辑。脉冲源产生时钟脉冲控制时序信号的发生和停止,实现对机器的启动与停机

- 时序信号产生部件。以时钟脉冲为基础,产生不同指令对应的周期、节拍、工作脉冲等时序信号,实现机器指令执行过程中的时序控制

- 操作控制信号形成部件。综合以上信号标志形成不同的控制信号,如读数据或者写数据

- 总线控制逻辑。实现对总线传输的控制,包括对数据和地址信息的缓冲和控制

中断和异常

内部异常:由CPU内部的异常引起的意外事件。如除0,断点,堆栈溢出,缺页

外部中断:外设完成任务或者发生某些特殊事件。每条指令执行完成后,CPU会主动查询有没有中断请求,如果有,则将下一条地址作为断点保存,然后转到用来处理相应中断事件的“中断服务程序“执行。

中断和异常都会破坏流水线的执行,造成流水线堵塞

数据通路基本结构和工作原理

数据通路:指令执行过程中数据所经过的路径

基本结构

组合逻辑元件(操作元件):

如MUX(多路选择器),Adder(加法器),ALU(算数逻辑部件),Decoder(译码器)

时序逻辑元件(存储元件):

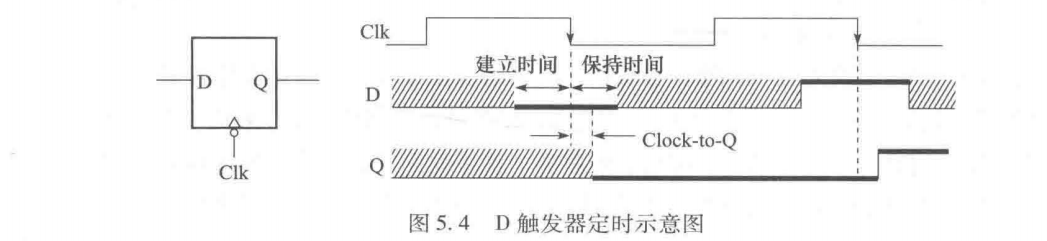

具有存储功能,如D触发器,输入状态在时钟控制下被写入到电路中,并保持电路的输出值不变,直到下一个时钟到达。输入端状态由时钟决定何时被写入

输入状态改变发生在时钟下降沿,需要经过建立时间和保持时间

输出端状态改变需要经过Clock-to-Q,即锁存延迟。该时间远小于保存时间

寄存器是状态存储元件,由n个D触发器组成一个n位寄存器

数据通路的时序控制

现代计算机中,定时信号就是时钟信号,一个时钟周期就是一个节拍。

只有状态元件能够存储信息,所有操作元件都必须从状态元件接收输入,并将输出写入状态元件中。而所有状态元件在同一个时钟信号控制下写入信息。

数据通路的时钟周期:Cycle Time = Clk-to-Q + Longest Delay + 建立时间 + 时钟偏移(可参考上图理解)

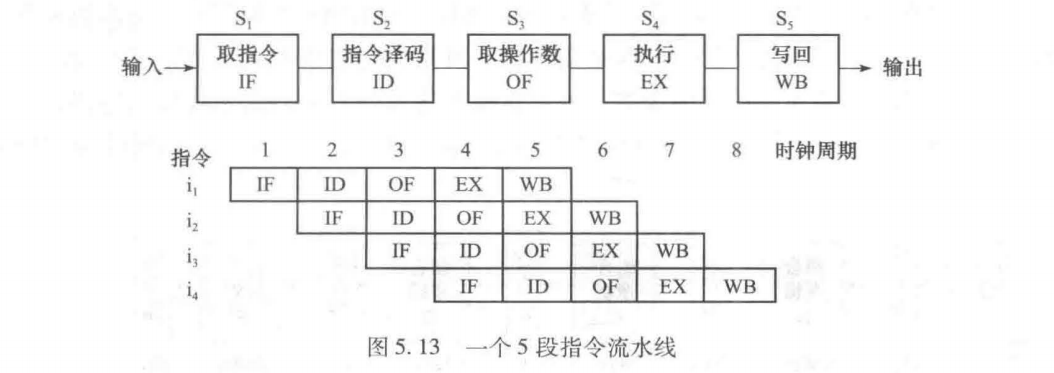

流水线指令执行

理想情况下,每个时钟周期都有一条指令进入流水线

流水线数据通路设计准则:指令流水段个数以最复杂指令所用的功能段个数为准;流水段的长度以最复杂功能段的操作所用时间为准

适合流水线的指令集特征:

- 指令长度应该尽量一致。有利于取指和译码

- 指令格式尽量规整,保证源操作数寄存器的位置相同,如都在指令的第25

21位和2016位 - 采用load/store风格,即只有这两个指令和存储器交互

- 数据和指令要对齐存放。有利于减少访存次数,因为CPU每次取数据是按照对齐位来取的

CISC指令集

复杂指令集,主要被Intel使用,缺点是不适用指令流水线,需要翻译成多个RISC的微操作

RISC指令集

精简指令集,多用在嵌入式设备和移动端设备,采用流水线的方式执行指令

指令流水线的实现

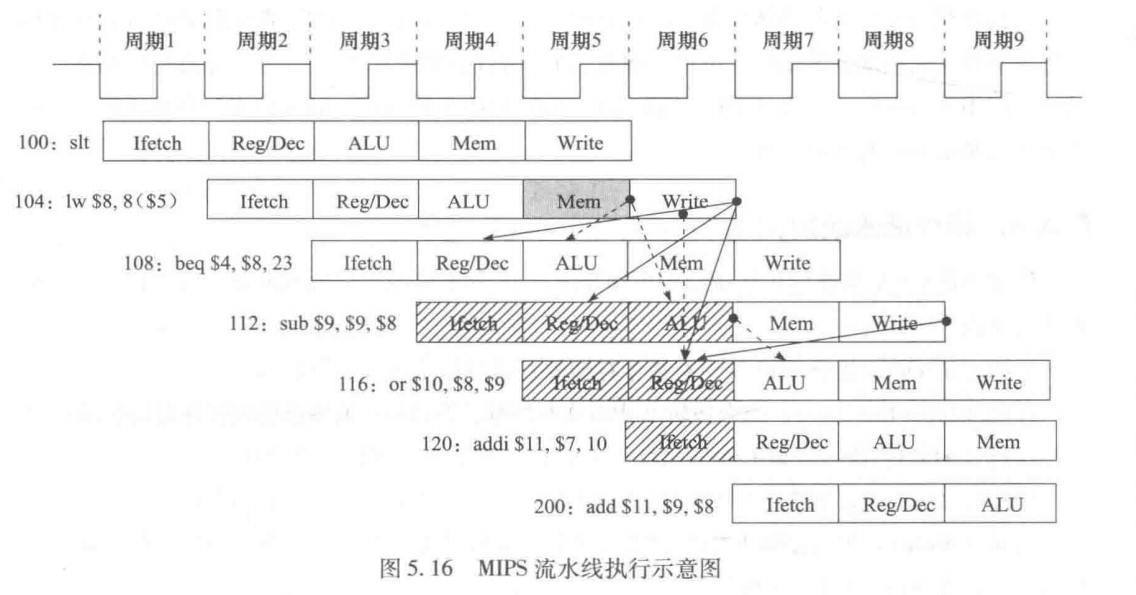

流水线冒险:一些情况可能使得流水线无法正确、按时执行后续指令,从而引起流水线阻塞或者停顿

- 结构冒险。硬件资源冲突,同一个部件被多个指令使用,可以通过引入告诉缓冲存储器(cache)避免访存冲突

- 数据冒险。后面指令用到前面指令的运算结果时,前面指令的结果还没有产生。可以添加nop延迟指令执行

- 控制冒险。指令执行顺序被改变,最常见的分支跳转

高级流水线技术:

超流水线:增加流水线级数

多发射流水线:同时启动多条指令